- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT82V3285AEQG (IDT, Integrated Device Technology Inc)IC PLL WAN SE STRATUM 100TQFP

IDT82V3285A

WAN PLL

Programming Information

120

August 7, 2009

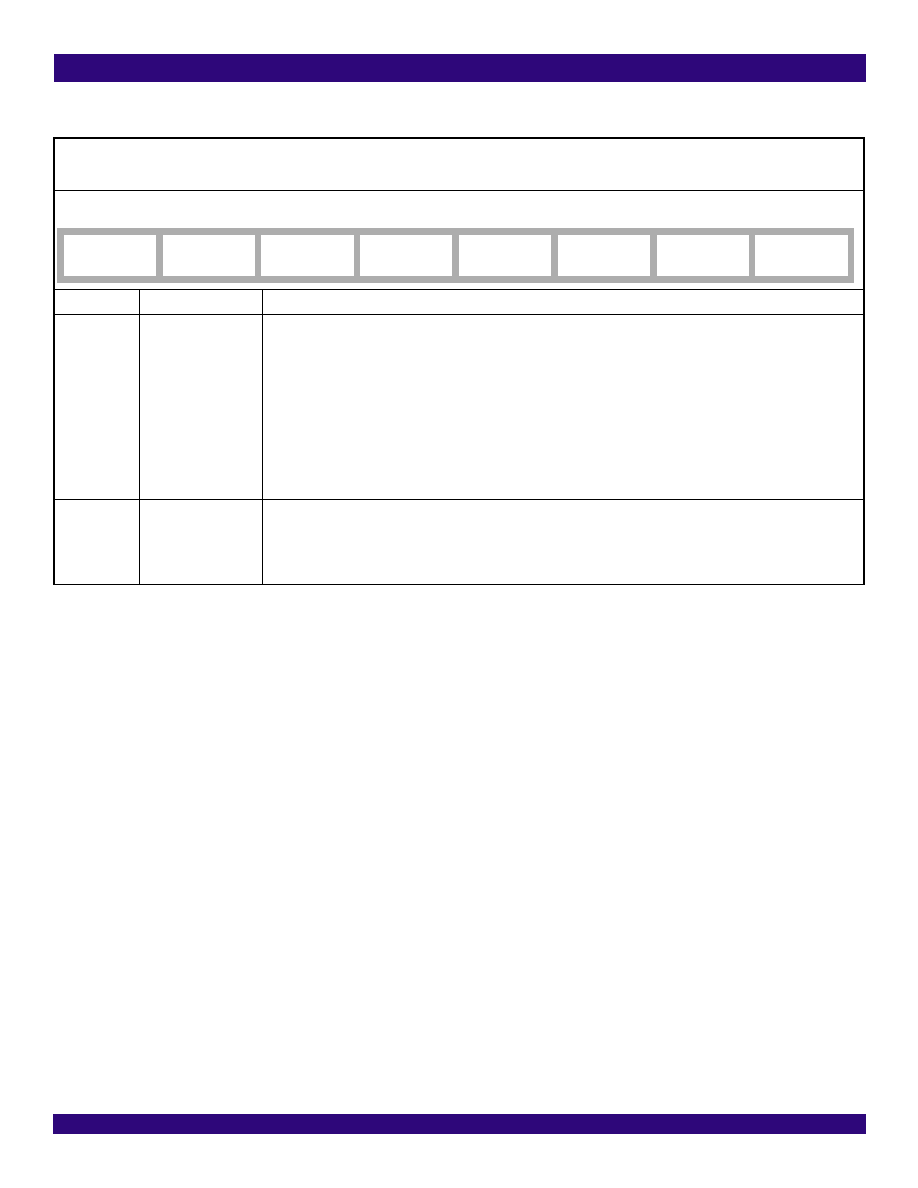

OUT3_FREQ_CNFG - Output Clock 3 Frequency Configuration

Address: 6FH

Type: Read / Write

Default Value: 00000100

Bit

Name

Description

7 - 4

OUT3_PATH_SEL[3:0]

These bits select an input to OUT3.

0000 ~ 0011: The output of T0 APLL. (default: 0000)

0100: The output of T0 DPLL 77.76 MHz path.

0101: The output of T0 DPLL 12E1/24T1/E3/T3 path.

0110: The output of T0 DPLL 16E1/16T1 path.

0111: The output of T0 DPLL GSM/OBSAI/16E1/16T1 path.

1000 ~ 1011: The output of T4 APLL.

1100: The output of T4 DPLL 77.76 MHz path.

1101: The output of T4 DPLL 12E1/24T1/E3/T3 path.

1110: The output of T4 DPLL 16E1/16T1 path.

1111: The output of T4 DPLL GSM/GPS/16E1/16T1 path.

3 - 0

OUT3_DIVIDER[3:0]

These bits select a division factor of the divider for OUT3.

The output frequency is determined by the division factor and the signal derived from T0/T4 DPLL or T0/T4 APLL output

(selected by the OUT3_PATH_SEL[3:0] bits (b7~4, 6FH)). If the signal is derived from one of the T0/T4 DPLL outputs,

please refer to Table 24 for the division factor selection. If the signal is derived from the T0/T4 APLL output, please refer to

Table 25 for the division factor selection.

76543210

OUT3_PATH_S

EL3

OUT3_PATH_S

EL2

OUT3_PATH_S

EL1

OUT3_PATH_S

EL0

OUT3_DIVIDER

3

OUT3_DIVIDER

2

OUT3_DIVIDER

1

OUT3_DIVIDER

0

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT82V3285EQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3288BCG

IC PLL WAN 3E STRATUM 2 208CABGA

IDT82V3355EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDT82V3358EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDTCSPT857DNLG8

IC PLL CLK DVR SDRAM 40-VFQFPN

IDTCV105EPVG8

IC CLK GEN DESKTOP PC 48-SSOP

IDTCV110NPVG

IC FLEXPC CLK PROGR P4 56-SSOP

IDTCV115-2PVG

IC FLEXPC CLK PROGR P4 56-TSSOP

相关代理商/技术参数

IDT82V3285AEQG8

制造商:Integrated Device Technology Inc 功能描述:IC PLL WAN SE STRATUM 100TQFP

IDT82V3285DQG

功能描述:IC PLL WAN STRATUM 100-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3285DQGT

功能描述:IC PLL WAN STRATUM 100-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3285EQG

功能描述:IC PLL WAN SE STRATUM 100TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3285EQG8

制造商:Integrated Device Technology Inc 功能描述:IC PLL WAN SE STRATUM 100TQFP

IDT82V3288

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3288BC

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3288BCG

功能描述:IC PLL WAN 3E STRATUM 2 208CABGA RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT